本设计中,ADC作为一般锁相环的鉴相器使用。 鉴相器验证实验框图如下: 后续实验:输入时钟fs不变,取不同的fx值,最后输出的复原频率也符合fo=fx-fs的关系。

基于数字化线性比相技术的锁相环

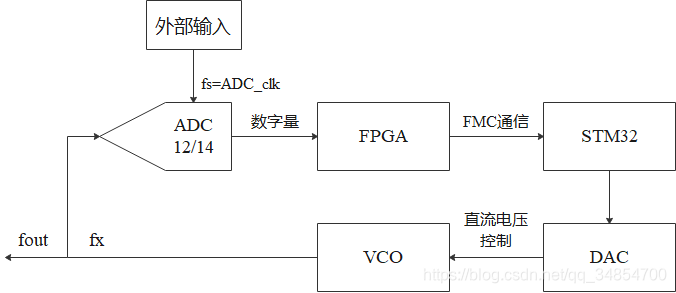

系统框图

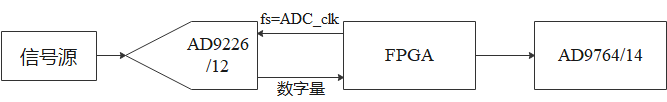

鉴相器

基本思路

其中,外部输入信号(fs=10MHz-1MHz)作为ADC的驱动时钟,压控振荡器VCO产生的(fx=10MHz)作为ADC的输入信号。

即,用fs锁fx,最后输出fout即为所求锁相输出频率信号。

//

理论支持:当ADC的输入时钟频率fs小于被采信号频率fx时,ADC输出的数字量的频率为:fx-fs,这种现象也被称为下变频,且两信号的频率差越大,下变频效果越明显;

理论上,当fx=fs时,如果两信号频率稳定度及相位噪声足够好时,输出的数字量频率为fx-fs=0Hz,即为一稳定的直流信号。ADC线性鉴相器验证

实验中,选用12位的AD9226进行采样处理,输入时钟为fs=10MHz-1MHz,输入信号设置为fx=10MHz,通过14位的DAC——AD9764将AD数字量进行复原,以验证ADC下变频功能。

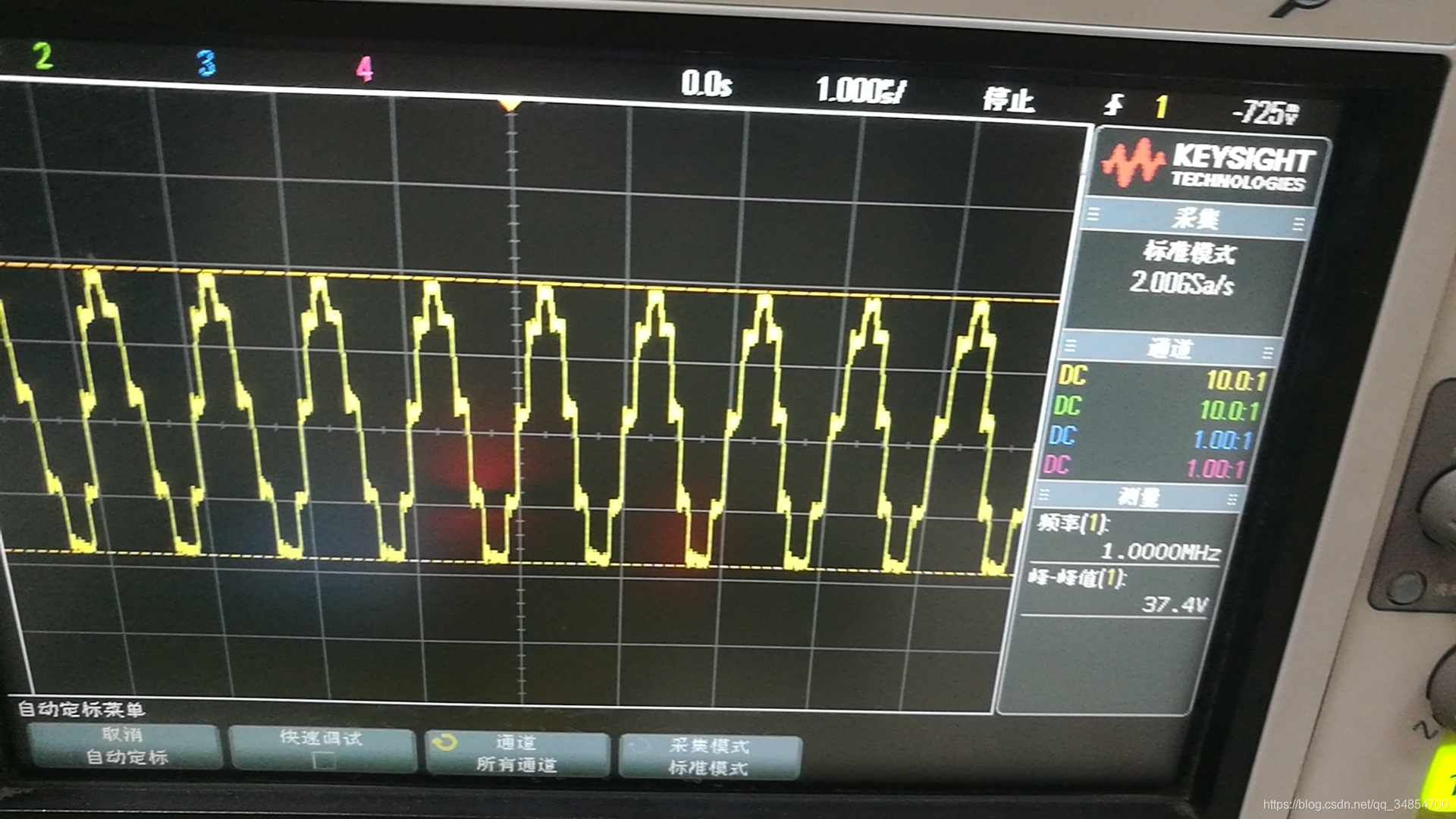

根据下变频理论,DA输出的信号频率应为:fo=fx-fs=1MHz

实验效果如下:

可以从示波器中观察到下变频之后的信号频率为1MHz,得证。(实验室示波器是坏的,所以峰峰值是诡异的37V……其实真实值是3V左右,师姐忽略就好)

量化误差:实验中输出信号有明显的量化误差(会芳师姐一直想看的东东~),这是因为AD9226是12位的,在高频处的复原效果并不好,后期可用14位的AD代替

频率稳定度误差:在实验过程中,当fs=10M-1Hz,fx=10MHz时,DA理论上应输出稳定的1Hz正弦波,但实际上却是几百赫兹左右的正弦波,且微调fx后,输出也不会有变化。经过反复测试,当fx-fs的精度大于1kHz时,DA输出才会和输入有明显的线性关系。

初步分析误差产生的原因为FPGA板载晶振、实验室信号发生器本身的频率稳定度过低(10-6左右),后期的实验中,至少FPGA需要外接原子钟或者8607,以保证精密锁相(如果只是MHz级别的锁相,现在的实验条件就足够了)。后续工作

例:参照系统框图,比如要求9M锁10M,即fs=9M,fx=10M,则AD输出数字量表示的频率为1M。当fx变大时,AD输出数字量表示的频率就会大于1M,这时控制STM32减小DA输出的电压,把VCO频率往下拉,fx就又稳到10M了,其他变化以此类推。

本网页所有视频内容由 imoviebox边看边下-网页视频下载, iurlBox网页地址收藏管理器 下载并得到。

ImovieBox网页视频下载器 下载地址: ImovieBox网页视频下载器-最新版本下载

本文章由: imapbox邮箱云存储,邮箱网盘,ImageBox 图片批量下载器,网页图片批量下载专家,网页图片批量下载器,获取到文章图片,imoviebox网页视频批量下载器,下载视频内容,为您提供.

阅读和此文章类似的: 全球云计算

官方软件产品操作指南 (170)

官方软件产品操作指南 (170)